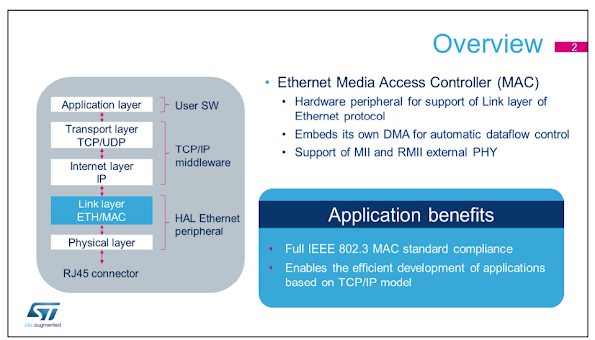

STM32H7-ETH

STM32H7’s Ethernet MAC peripheral

- The MAC is in charge of the Link layer of TCP/IP communication model.

- Upper layers are managed by software. For example, Transport and Internet layers can be managed by the popular Light weight IP stack.

- the physical layer, or PHY, is supported by external components and linked to an RJ45 connector.

The key features of the STM32H7 Ethernet MAC peripheral :

The peripheral supports both full- and half-duplex modes of

operation at either 10 or 100 Mbit/s. Auto-negotiation

between the peripheral and the external PHY enables

automatic configuration of the operation mode.

** Duplex : The term duplex is used to describe a communication channel that can carry signals in both directions, unlike a simplex channel, which carries a signal in only one direction .

** Half-duplex communication : is a one-way data flow, which means that data can only work in one direction at a time. Data is not sent and received at the same time.

** Full-duplex communication :The data flow is therefore bidirectional, and the data can be sent and received at the same time. Most network cards that are sold today are full-duplex.

It is like a telephone call, because each person can speak and hear what the other person is saying simultaneously .

The external

PHY is supported through two interface types: The typical

Media-Independent Interface, or MII, and the Reduced-MII

interface that needs half the pins of the MII.

** MII : each PHY requires 18 signals to communicate with the MAC, and only 2 of these signals can be shared among multiple PHY devices.

** RMII (reduced MII) : was developed as a variant of MII to cut the number of unshareable signals per PHY interface in half (down to 8 per PHY).The RMII specification is also capable of supporting 10 Mbps and 100 Mbps data rates. In RMII, the clock frequency used in the PHY runs continuously at 50 MHz for both 10 Mbps and 100 Mbps data rates.

The external PHY is controlled by the peripheral through

the Station Management Interface (SMI) that allows read

and write access to PHY internal registers. This interface

supports the MDIO protocol on a pair of wires. Read and

Write operation codes are available.

Commentaires

Enregistrer un commentaire